January 2014

# Study and implementation of RL78 low power mode

Application note

Emeric Bartholin GE5 YEARS 2013-2014

## Summary

| Introduct | tion                         | 2 |

|-----------|------------------------------|---|

| 1. Ir     | nternal architecture of RL78 | 3 |

| 2. T      | he three mode of low power   | 4 |

| 2.1       | HALT mode                    | 5 |

| 2.2       | STOP mode                    | 5 |

| 2.3       | SNOOZE mode                  | 7 |

| Annex     |                              | 7 |

|           |                              |   |

## Introduction

This application note describe the different operating mode of the microcontroller RL78 which made by the company Renesas. Renesas are a Japanese company leader on the microcontroller market. This company employed 25000 salaries in several country.

The microcontroller RL78 are the true lower power microcontroller of Renesas. It's a polyvalent microcontroller specialize for applications with a strong constraint of electrical consummation.

The RL78 are available in several release (G12, G13, G14...) with more or less peripheries, more or less evolved.

## 1. Internal architecture of RL78G14

| Safety<br>RAM                    |                                        | 5-bit CPU<br>44DMIPS          |  |  |

|----------------------------------|----------------------------------------|-------------------------------|--|--|

| Parity Check                     | MUL/DIV/MA                             | C Instruction                 |  |  |

| ADC<br>Self-diagnostic           | Four Regi                              | ster Banks                    |  |  |

| Clock<br>Monitoring              | 16-bit Ba                              | rrel Shifter                  |  |  |

| Memory<br>CRC                    | Memory                                 | Power Management              |  |  |

| I/O Port<br>Read back            | Program Flash<br>up to 256KB           | HALT<br>RTC, DTC Enabled      |  |  |

| Timers                           | SRAM<br>up to 24KB                     | SNOOZE<br>Serial, ADC Enabled |  |  |

| Timer Array<br>16-bit, 8ch       | Data Flash<br>8KB                      | STOP<br>SRAM On               |  |  |

| Timer RD<br>16-bit, 2ch          | Communication                          | Analog                        |  |  |

| Timer RG<br>16-bit, 1ch          | 8 x I <sup>2</sup> C<br>Master         | ADC<br>10-bit, 20ch           |  |  |

| Timer RJ<br>16-bit, 1ch          | 2 x I <sup>2</sup> C<br>Multi-Master   | Internal Vref.                |  |  |

| Interval Timer<br>12-bit, 1ch    | 8 x CSI / SPI<br>7-, 8-bit             | Temp. Sensor                  |  |  |

| WDT<br>17-bit , 1ch              | 4 x UART<br>7-, 8-, 9-bit              | D/A<br>8-bit, 2ch             |  |  |

| RTC<br>Calendar                  | 1 x LIN<br>1ch                         | Comparator<br>2ch             |  |  |

| System                           |                                        |                               |  |  |

| DTC<br>24ch                      | Clock Generation<br>Internal, External | ELC<br>26 events              |  |  |

| Interrupt Controller<br>4 Levels | POR, LVD                               | Debug w/ trace<br>Single-Wire |  |  |

The figure following present the internal contents of the microcontroller RL78G14.

Figure 1: internal architecture of RL78G14

On this figures we can see the diversity of the available peripheries of the RL78 G14.

They are several timer for all application input capture, PWM, delay... They also have communication module and analog module with a 10 bits analog converter. This microcontroller are flash memory dedicate for storage data and 24 channel of data transfers controller for automatize memory transfer.

### 2. <u>The three mode of low power</u>

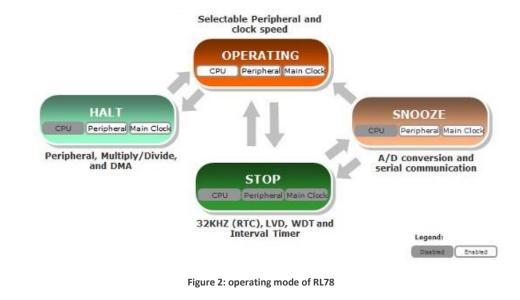

The RL78 are four different mode of operation which describe by the following figure.

The RL78 also has 4 different operating mode:

- Mode "operating" the microcontroller is in normal operation mode is more about consuming 1.2mA.

- In "Halt" mode the heart of the microcontroller are stop but a lot of peripheries are available. Halt mode are the intermediate mode and reduces power consumption to approximately 0.5mA this value depends on the number of peripheries used by the application.

- The "Stop" mode is the ultimate mode of the point of view of power consumption. This mode stopped all the microcontroller and peripheries unless some timer and interrupt pin to wake up the microcontroller. This mode reduce power consumption of the microcontroller about 0.0005mA.

- The "SNOOZE" mode permit to maximize the time in Stop mode when the application use A/D converter or serial communication because this mode permit to wake up peripheries just during the time they need and switch automatically in STOP mode without using of CPU.

## 2.1 <u>HALT mode</u> 2.1.1 <u>Detaille description</u>

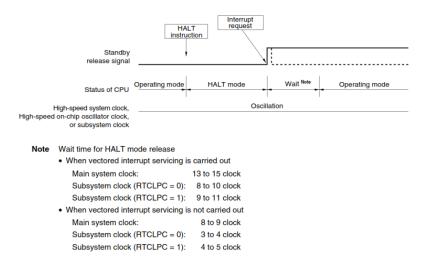

The first mode of standby function is "Halt". In Halt mode the CPU operation clock is stopped but the clock of using peripheries still on. In this mode, the operating current is not decreased as much as stop mode, but halt mode is effective for restarting operation immediately after an interrupt request.

Figure 3: Halt mode Release by interrupt request

For set HALT mode you must execute HALT instruction. For example with IAR compiler insert in your code this line "HALT ();" or the intrinsic function "\_halt();".

Halt mode is best mode if you want to restart CPU operation quickly and for use peripheries without CPU.

#### 2.1.2 Operable peripheries during Halt mode

As mention before halt mode stop operation of the CPU operation but not peripheries with certain condition. All peripheries enable before the setting of HALT mode still on.

Operable peripheries during HALT mode:

- DTC (Data transfer controleur)

- ALL timer

- ADC and DAC

- Serial interface

- RAM and RAM control function are operable with a DTC or stop

- See annex for more information

If the CPU operate on the subsystem clock and if low consumption RTC mode is active the following peripheries are disable:

- ADC, DAC

- serial interface,

- DTC

- Timer array unit, Timer RJ, RG, RD

- 2.2 <u>STOP mode</u> 2.2.1 Detaille description

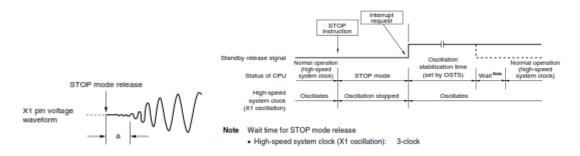

To minimize the electric consummation you must use STOP mode. In this mode the high-speed system clock oscillator and high-speed on-chip oscillator stop, stopping the whole system, thereby considerably reducing the CPU operating current. This mode can be clear by an interrupt request but restarting the main clock needs a waiting time for clock stabilization.

Figure 4: Clock stabilization and STOP mode Release by interrupt request

To set STOP mode you must have to execute STOP instruction. For example with IAR compiler insert in your code this line "STOP ();" or the intrinsic function "\_stop();".Caution the stop instruction is not execute during data flash programming.

To resume the restart time for STOP mode are longer than HALT mode but STOP mode operating current are less than HALT mode.

#### 2.2.2 Operable peripheries during STOP mode

In STOP mode the main clock of the system are stop this implies some peripheries are stop too. Some peripheries still operable during STOP mode but you must active them before entering stop mode:

- RTC, interval timer

- Watchdog timer

- Power-on reset

- External interrupt and Key interrupt

## 2.3 <u>SNOOZE mode</u> 2.3.1 Detaille description

SNOOZE mode is use when you wait a data reception or A/D conversion request by and interrupt signal the end of the reception or the conversion is the source of a DTC. So STOP mode are clear by the first interrupt the conversion or reception are execute and the result store by the DTC and after this STOP mode are set automatically without CPU operating.

SNOOZE mode can be used only if your system use the high-speed on-chip oscillator for main clock.

To set SNOOZE mode you must have to set up serial standby control register (SSCm) before switching to STOP mode for serial unit. For A/D converter you have to set up A/D converter mode register (ADM2) before switching to STOP mode.

## Annex

| _                                                                                                                                                                                                                                                                                                                                                                              | - HALTI                                | Node Setting | When HALT Instruction is                                                 | s Executed While CPU is Operat                              | ing on Main System Clock                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--------------|--------------------------------------------------------------------------|-------------------------------------------------------------|--------------------------------------------|

| HALT Mode Setting                                                                                                                                                                                                                                                                                                                                                              |                                        |              | When CPU is Operating on                                                 | When CPU is Operating on                                    | When CPU is Operating on                   |

|                                                                                                                                                                                                                                                                                                                                                                                |                                        |              | High-speed On-chip Oscillator                                            | X1 Clock (fx)                                               | External Main System Clock                 |

| Item                                                                                                                                                                                                                                                                                                                                                                           |                                        |              | Clock (fH)                                                               |                                                             | (fex)                                      |

| System clock                                                                                                                                                                                                                                                                                                                                                                   |                                        |              | Clock supply to the CPU is stop                                          | ped                                                         |                                            |

|                                                                                                                                                                                                                                                                                                                                                                                | Main system clock                      | tH.          | Operation continues (cannot Operation disabled<br>be stopped)            |                                                             |                                            |

|                                                                                                                                                                                                                                                                                                                                                                                |                                        | tx           | Operation disabled                                                       | Operation continues (cannot<br>be stopped)                  | Cannot operate                             |

|                                                                                                                                                                                                                                                                                                                                                                                |                                        | fex          |                                                                          | Cannot operate                                              | Operation continues (cannot<br>be stopped) |

|                                                                                                                                                                                                                                                                                                                                                                                | Subsystem clock                        | ter          | Status before HALT mode was                                              | set is retained                                             |                                            |

|                                                                                                                                                                                                                                                                                                                                                                                | -                                      | fexs         |                                                                          |                                                             |                                            |

|                                                                                                                                                                                                                                                                                                                                                                                | fi.                                    | •            | Set by bits 0 (WDSTBYON) and<br>operation speed mode control r           | 4 (WDTON) of option byte (000<br>egister (OSMC)             | C0H), and WUTMMCK0 bit of                  |

|                                                                                                                                                                                                                                                                                                                                                                                |                                        |              | WUTMMCK0 = 1: Oscillates                                                 |                                                             |                                            |

|                                                                                                                                                                                                                                                                                                                                                                                |                                        |              | WUTMMCK0 = 0 and WDTON                                                   |                                                             |                                            |

|                                                                                                                                                                                                                                                                                                                                                                                |                                        |              | <ul> <li>WUTMMCK0 = 0, WDTON =</li> <li>WUTMMCK0 = 0, WDTON =</li> </ul> | 1, and WDSTBYON = 1: Oscillat<br>1, and WDSTBYON = 0: Stops | cs                                         |

| CP                                                                                                                                                                                                                                                                                                                                                                             | v                                      |              | Operation stopped                                                        |                                                             |                                            |

| Co                                                                                                                                                                                                                                                                                                                                                                             | de flash memory                        |              |                                                                          |                                                             |                                            |

| -                                                                                                                                                                                                                                                                                                                                                                              | ta flash memory                        |              |                                                                          |                                                             |                                            |

| RA                                                                                                                                                                                                                                                                                                                                                                             | м                                      |              | Operation stopped (Operable w                                            | hile in the DTC is executed)                                |                                            |

| Po                                                                                                                                                                                                                                                                                                                                                                             | rt (latch)                             |              | Status before HALT mode was                                              | set is retained                                             |                                            |

| Tin                                                                                                                                                                                                                                                                                                                                                                            | ner array unit                         |              | Operable                                                                 |                                                             |                                            |

| Re                                                                                                                                                                                                                                                                                                                                                                             | al-time clock (RTC)                    |              |                                                                          |                                                             |                                            |

| 12-                                                                                                                                                                                                                                                                                                                                                                            | bit interval timer                     |              |                                                                          |                                                             |                                            |

| Wa                                                                                                                                                                                                                                                                                                                                                                             | stchdog timer                          |              | See CHAPTER 13 WATCHDOG TIMER                                            |                                                             |                                            |

| Timer BJ                                                                                                                                                                                                                                                                                                                                                                       |                                        |              | Operable                                                                 |                                                             |                                            |

| Tin                                                                                                                                                                                                                                                                                                                                                                            | ner RD                                 |              |                                                                          |                                                             |                                            |

| Tin                                                                                                                                                                                                                                                                                                                                                                            | ner RG                                 |              |                                                                          |                                                             |                                            |

| Clo                                                                                                                                                                                                                                                                                                                                                                            | ck output/buzzer ou                    | tput         |                                                                          |                                                             |                                            |

| A/t                                                                                                                                                                                                                                                                                                                                                                            | D converter                            |              |                                                                          |                                                             |                                            |

| D//                                                                                                                                                                                                                                                                                                                                                                            | A converter Note                       |              |                                                                          |                                                             |                                            |

| Co                                                                                                                                                                                                                                                                                                                                                                             | mparator New                           |              |                                                                          |                                                             |                                            |

| Se                                                                                                                                                                                                                                                                                                                                                                             | rial array unit (SAU)                  |              |                                                                          |                                                             |                                            |

|                                                                                                                                                                                                                                                                                                                                                                                | rial interface (IICA)                  |              |                                                                          |                                                             |                                            |

| DT                                                                                                                                                                                                                                                                                                                                                                             | C                                      |              | Operable                                                                 |                                                             |                                            |

| EL                                                                                                                                                                                                                                                                                                                                                                             |                                        |              | Operable function blocks can b                                           | e linked                                                    |                                            |

|                                                                                                                                                                                                                                                                                                                                                                                | wer-on-reset function                  |              | Operable                                                                 |                                                             |                                            |

|                                                                                                                                                                                                                                                                                                                                                                                | Itage detection funct                  | ion          |                                                                          |                                                             |                                            |

|                                                                                                                                                                                                                                                                                                                                                                                | ternal interrupt                       |              |                                                                          |                                                             |                                            |

| _                                                                                                                                                                                                                                                                                                                                                                              | y interrupt function                   | ed CBC       |                                                                          |                                                             |                                            |

|                                                                                                                                                                                                                                                                                                                                                                                | Coperation High-spe<br>ction General-r | ourpose CRC  | Operation stopped (Operable w                                            | bile in the DTC is executed)                                |                                            |

|                                                                                                                                                                                                                                                                                                                                                                                | Generary                               |              |                                                                          | ,                                                           |                                            |

| Illegal-memory access detection function<br>RAM parity check function                                                                                                                                                                                                                                                                                                          |                                        |              | Operation stopped (Operable w                                            | the in the bird is executed)                                |                                            |

| RAM guard function                                                                                                                                                                                                                                                                                                                                                             |                                        |              |                                                                          |                                                             |                                            |

|                                                                                                                                                                                                                                                                                                                                                                                | R guard function                       |              |                                                                          |                                                             |                                            |

| Note         Only for products with 96 KB or more code flash memory.           Remark         Operation stopped:<br>Operation disabled:         Operation is automatically stopped before switching to the HALT mode.           fm:         High-speed on-chip oscillator clock<br>fx:         X1 clock<br>fxr:         fm:         Low-speed on-chip oscillator clock<br>fxr: |                                        |              |                                                                          |                                                             | oscillator clock<br>em clock               |

| Table 23-1. | Operating Statuses in HALT Mode (1 | /2) |

|-------------|------------------------------------|-----|

|-------------|------------------------------------|-----|

| Table 23-1. | Operating | Statuses i | in HALT | Mode ( | (2/2) |  |

|-------------|-----------|------------|---------|--------|-------|--|

|-------------|-----------|------------|---------|--------|-------|--|

| ~                                        |                                           |                                           |                                                                                                                           |                                                             |  |

|------------------------------------------|-------------------------------------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--|

| HALT Mode Setting                        |                                           | Mode Setting                              | When HALT Instruction Is Executed White                                                                                   | le CPU Is Operating on Subsystem Clock                      |  |

| Item                                     |                                           |                                           | When CPU is Operating on XT1 Clock (fxr)                                                                                  | When CPU Is Operating on External<br>Subsystem Clock (fexs) |  |

| System clock                             |                                           |                                           | Clock supply to the CPU is stopped                                                                                        |                                                             |  |

| Main sys                                 | tem clock                                 | fin                                       | Operation disabled                                                                                                        |                                                             |  |

|                                          |                                           | fx                                        |                                                                                                                           |                                                             |  |

|                                          |                                           | fex                                       |                                                                                                                           |                                                             |  |

| Subsyste                                 | m clock                                   | fxr                                       | Operation continues (cannot be stopped)                                                                                   | Cannot operate                                              |  |

|                                          |                                           | fexs                                      | Cannot operate                                                                                                            | Operation continues (cannot be stopped)                     |  |

| fiL.                                     |                                           |                                           | Set by bits 0 (WDSTBYON) and 4 (WDTON) of                                                                                 | option byte (000C0H), and WUTMMCK0 bit of                   |  |

|                                          |                                           |                                           | operation speed mode control register (OSMC)                                                                              |                                                             |  |

|                                          |                                           |                                           | <ul> <li>WUTMMCK0 = 1: Oscillates</li> </ul>                                                                              |                                                             |  |

|                                          |                                           |                                           | WUTMMCK0 = 0 and WDTON = 0: Stops                                                                                         |                                                             |  |

|                                          |                                           |                                           | <ul> <li>WUTMMCK0 = 0, WDTON = 1, and WDSTBY</li> <li>WUTMMCK0 = 0, WDTON = 1, and WDSTBY</li> </ul>                      |                                                             |  |

| CPU                                      |                                           |                                           | Operation stopped                                                                                                         |                                                             |  |

| Code flash m                             | emory                                     |                                           |                                                                                                                           |                                                             |  |

| Data flash m                             |                                           |                                           |                                                                                                                           |                                                             |  |

| RAM                                      |                                           |                                           | Operation stopped (Operable while in the DTC I                                                                            | is executed)                                                |  |

|                                          |                                           |                                           | Status before HALT mode was set is retained                                                                               | a sourceffed)                                               |  |

| Port (latch)<br>Timer array u            | init                                      |                                           | Operable (Operation is disabled while in the low                                                                          | consumption BTC mode (when the BTC) PC                      |  |

| rimer array c                            | 21 ML                                     |                                           | bit of the OSMC register is 1))                                                                                           | Consumption ATC mode (when the ATCCPC                       |  |

| Real-time clo                            | ck (BTC)                                  |                                           | Operable                                                                                                                  |                                                             |  |

| 12-bit interva                           |                                           |                                           | openand                                                                                                                   |                                                             |  |

| Watchdog tin                             |                                           |                                           | See CHAPTER 13 WATCHDOG TIMER                                                                                             |                                                             |  |

| Timer RJ                                 |                                           |                                           | Operable (Operation is disabled while in the low consumption RTC mode (when the RTCLPC                                    |                                                             |  |

| Timer RD                                 |                                           |                                           | bit of the OSMC register is 1))                                                                                           |                                                             |  |

| Timer RG                                 |                                           |                                           |                                                                                                                           |                                                             |  |

|                                          |                                           |                                           |                                                                                                                           |                                                             |  |

| Clock output                             |                                           | tput                                      | Constitute disability                                                                                                     |                                                             |  |

| A/D converte                             | Note                                      |                                           | Operation disabled<br>Operable (Operation is disabled while in the low consumption RTC mode (when the RTCLPC              |                                                             |  |

| D/A converte                             |                                           |                                           | bit of the OSMC register is 1))                                                                                           |                                                             |  |

| Comparator                               |                                           |                                           |                                                                                                                           |                                                             |  |

| Serial array u                           |                                           |                                           | Constant dealerst                                                                                                         |                                                             |  |

| Serial Interfa                           | ce (IICA)                                 |                                           | Operation disabled                                                                                                        |                                                             |  |

| DTC                                      |                                           |                                           | Operable (Operation is disabled while in the low consumption RTC mode (when the RTCLPC<br>bit of the OSMC register is 1)) |                                                             |  |

| ELC                                      |                                           |                                           | Operable function blocks can be linked                                                                                    |                                                             |  |

| Power-on-res                             | set function                              | n                                         | Operable                                                                                                                  |                                                             |  |

| Voltage dete                             | ction funct                               | lon                                       |                                                                                                                           |                                                             |  |

| External interrupt                       |                                           |                                           |                                                                                                                           |                                                             |  |

| Key interrupt                            | function                                  |                                           |                                                                                                                           |                                                             |  |

| CRC operation High-speed CRC             |                                           | ed CRC                                    | Operation disabled                                                                                                        |                                                             |  |

| function                                 | General-p                                 | purpose CRC                               | Operation stopped (Operable while in the DTC I                                                                            | is executed)                                                |  |

| lliegal-memory access detection function |                                           | ection function                           | Operation stopped (Operable while in the DTC is executed)                                                                 |                                                             |  |

| RAM parity check function                |                                           |                                           |                                                                                                                           |                                                             |  |

| RAM guard function                       |                                           |                                           |                                                                                                                           |                                                             |  |

| SFR guard fu                             | unction                                   |                                           |                                                                                                                           |                                                             |  |

| Remark O<br>O<br>fire<br>fx:             | peration a<br>peration of<br>High<br>X1 d | stopped: (<br>disabled: (<br>-speed on-cl | fex: Exter                                                                                                                |                                                             |  |

| <                          |               |                 | Table 25-2. Operating of                                                                                                                                                                                                                                                                                                  |                                           |                                                                 |  |

|----------------------------|---------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-----------------------------------------------------------------|--|

| STOP Mode Setting          |               |                 |                                                                                                                                                                                                                                                                                                                           | Executed While CPU is Operat              |                                                                 |  |

| Item                       |               |                 | When CPU Is Operating on<br>High-speed On-chip Oscillator<br>clock (1H)                                                                                                                                                                                                                                                   | When CPU is Operating on<br>X1 Clock (fx) | When CPU Is Operating on<br>External Main System Clock<br>(ftx) |  |

| System clos                | ik 🛛          |                 | Clock supply to the CPU is stop                                                                                                                                                                                                                                                                                           | ped                                       |                                                                 |  |

| Main sy                    | stem clock    | fin             | Stopped                                                                                                                                                                                                                                                                                                                   |                                           |                                                                 |  |

|                            |               | fx              |                                                                                                                                                                                                                                                                                                                           |                                           |                                                                 |  |

|                            |               | fex             |                                                                                                                                                                                                                                                                                                                           |                                           |                                                                 |  |

| Subsys                     | em clock      | fxt             | Status before STOP mode was                                                                                                                                                                                                                                                                                               | set is retained                           |                                                                 |  |

|                            |               | fexis           |                                                                                                                                                                                                                                                                                                                           |                                           |                                                                 |  |

| ħL.                        |               |                 | Set by bits 0 (WDSTBYON) and 4 (WDTON) of option byte (000C0H), and WUTMMCK0 bit of<br>operation speed mode control register (OSMC)<br>• WUTMMCK0 = 1: Oscillates<br>• WUTMMCK0 = 0 and WDTON = 0: Stops<br>• WUTMMCK0 = 0, WDTON = 1, and WDSTBYON = 1: Oscillates<br>• WUTMMCK0 = 0, WDTON = 1, and WDSTBYON = 0: Stops |                                           |                                                                 |  |

| CPU                        |               |                 | Operation stopped                                                                                                                                                                                                                                                                                                         |                                           |                                                                 |  |

| Code flash                 | memory        |                 |                                                                                                                                                                                                                                                                                                                           |                                           |                                                                 |  |

| Data flash r               | nemory        |                 | Operation stopped (The STOP I                                                                                                                                                                                                                                                                                             | instruction is not executed during        | ) data flash programming)                                       |  |

| RAM                        |               |                 | Operation stopped                                                                                                                                                                                                                                                                                                         |                                           |                                                                 |  |

| Port (latch)               |               |                 | Status before STOP mode was set is retained                                                                                                                                                                                                                                                                               |                                           |                                                                 |  |

| Timer array                | unit          |                 | Operation disabled                                                                                                                                                                                                                                                                                                        |                                           |                                                                 |  |

| Real-time d                | lock (RTC)    |                 | Operable                                                                                                                                                                                                                                                                                                                  |                                           |                                                                 |  |

| 12-bit interv              | al timer      |                 |                                                                                                                                                                                                                                                                                                                           |                                           |                                                                 |  |

| Watchdog t                 | mer           |                 | See CHAPTER 13 WATCHDOG                                                                                                                                                                                                                                                                                                   | TIMER                                     |                                                                 |  |

| Timer RJ                   |               |                 | Wakeup by event counter mode operable                                                                                                                                                                                                                                                                                     |                                           |                                                                 |  |

| Timer RD                   |               |                 | Operation disabled                                                                                                                                                                                                                                                                                                        |                                           |                                                                 |  |

| Timer RG                   |               |                 |                                                                                                                                                                                                                                                                                                                           |                                           |                                                                 |  |

| Clock output               | t/buzzer ou   | tput            | Operable only when subsystem clock is selected as the count clock                                                                                                                                                                                                                                                         |                                           |                                                                 |  |

| A/D convert                | er            |                 | Wakeup operation is enabled (switching to the SNOOZE mode)                                                                                                                                                                                                                                                                |                                           |                                                                 |  |

| D/A convert                |               |                 | Operable (status before STOP mode was set is retained)                                                                                                                                                                                                                                                                    |                                           |                                                                 |  |

| Comparato                  | Note          |                 | Operable (when digital filter is not used)                                                                                                                                                                                                                                                                                |                                           |                                                                 |  |

| Serial array unit (SAU)    |               |                 | Wakeup operation is enabled only for CSIp and UARTq (switching to the SNOOZE mode)<br>Operation is disabled for anything other than CSIp and UARTq                                                                                                                                                                        |                                           |                                                                 |  |

| Serial Interf              | ace (IICA)    |                 | Wakeup by address match oper                                                                                                                                                                                                                                                                                              | able                                      |                                                                 |  |

| DTC                        |               |                 | Operation disabled                                                                                                                                                                                                                                                                                                        |                                           |                                                                 |  |

| ELC                        |               |                 | Operable function blocks can be                                                                                                                                                                                                                                                                                           | linked                                    |                                                                 |  |

| Power-on-re                | eset function | 1               | Operable                                                                                                                                                                                                                                                                                                                  |                                           |                                                                 |  |

| Voltage detection function |               |                 |                                                                                                                                                                                                                                                                                                                           |                                           |                                                                 |  |

| External Interrupt         |               |                 |                                                                                                                                                                                                                                                                                                                           |                                           |                                                                 |  |

| Key interrupt function     |               |                 |                                                                                                                                                                                                                                                                                                                           |                                           |                                                                 |  |

| CRC operation              | High-spec     | ed CRC          | Operation stopped                                                                                                                                                                                                                                                                                                         |                                           |                                                                 |  |

| function                   |               | urpose CRC      |                                                                                                                                                                                                                                                                                                                           |                                           |                                                                 |  |

| -                          |               | ection function |                                                                                                                                                                                                                                                                                                                           |                                           |                                                                 |  |

| RAM parity check function  |               |                 |                                                                                                                                                                                                                                                                                                                           |                                           |                                                                 |  |

| RAM guard                  |               |                 |                                                                                                                                                                                                                                                                                                                           |                                           |                                                                 |  |

| SFR guard function         |               |                 |                                                                                                                                                                                                                                                                                                                           |                                           |                                                                 |  |

#### Table 23-2. Operating Statuses in STOP Mode

Note Only for products with 96 KB or more code flash memory.

| -                      |                       |                                                                                                                                                             |  |  |  |

|------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| ST<br>Item             | OP Mode Setting       | During STOP mode, receiving data signal from CSIp and UARTq, inputting timer trigger signal<br>to A/D converter, and generating DTC activation by interrupt |  |  |  |

|                        |                       | When CPU is Operating on High-speed On-chip Oscillator Clock (fm)                                                                                           |  |  |  |

| System clock           |                       | Clock supply to the CPU is stopped                                                                                                                          |  |  |  |

| Main system o          | lock fin              | Operation started                                                                                                                                           |  |  |  |

|                        | fx                    | Stopped                                                                                                                                                     |  |  |  |

|                        | fex                   |                                                                                                                                                             |  |  |  |

| Subsystem clo          | ook fxr               | Use of the status while in the STOP mode continues                                                                                                          |  |  |  |

| ,                      | fexs                  |                                                                                                                                                             |  |  |  |

|                        | 1252                  | Set by bits 0 (WDSTBYON) and 4 (WDTON) of option byte (000C0H), and WUTMMCK0 bit of                                                                         |  |  |  |

| fiL.                   |                       | operation speed mode control register (OSMC)                                                                                                                |  |  |  |

|                        |                       | WUTMMCK0 = 1: Oscillates                                                                                                                                    |  |  |  |

|                        |                       | WUTMMCK0 = 0 and WDTON = 0: Stops     WUTMMCK0 = 0, WDTON = 1, and WDSTBYON = 1: Oscillates                                                                 |  |  |  |

|                        |                       | WUTMMCK0 = 0, WDTON = 1, and WDSTBYON = 1. Oscillates     WUTMMCK0 = 0, WDTON = 1, and WDSTBYON = 0: Stops                                                  |  |  |  |

| CPU                    |                       | Operation stopped                                                                                                                                           |  |  |  |

| Code flash memor       | ry .                  |                                                                                                                                                             |  |  |  |

| Data flash memory      | y                     |                                                                                                                                                             |  |  |  |

| RAM                    |                       | Operation stopped (Operable while in the DTC is executed)                                                                                                   |  |  |  |

| Port (latch)           |                       | Use of the status while in the STOP mode continues                                                                                                          |  |  |  |

| Timer array unit       |                       | Operation disabled                                                                                                                                          |  |  |  |

| Real-time clock (R     | TC)                   | Operable                                                                                                                                                    |  |  |  |

| 12-bit interval time   | ar -                  |                                                                                                                                                             |  |  |  |

| Watchdog timer         |                       | See CHAPTER 13 WATCHDOG TIMER                                                                                                                               |  |  |  |

| Timer RJ               |                       | Operation disabled                                                                                                                                          |  |  |  |

| Timer RD               |                       |                                                                                                                                                             |  |  |  |

| Timer RG               |                       |                                                                                                                                                             |  |  |  |

| Clock output/buzz      | er output             | Operable only when subsystem clock is selected as the count clock                                                                                           |  |  |  |

| A/D converter          |                       | Operable                                                                                                                                                    |  |  |  |

| D/A converter Note     |                       | Operable (Status before SNOOZE mode was set is retained)                                                                                                    |  |  |  |

| Comparator Nets        |                       | Operable (when digital filter is not used)                                                                                                                  |  |  |  |