# Commande d'un moteur pas à pas avec un hacheur

### Introduction

- Orientation de l'axe du moteur

- Boussole

- Principe :

- L'axe du moteur devra suivre le nord magnétique

- L'axe du moteur devra suivre une direction voulue

### Sommaire

- Première étude

- Commande du moteur

- Boussole

- Potentiomètre et CAN

- Timer variable

- Ecran LCD

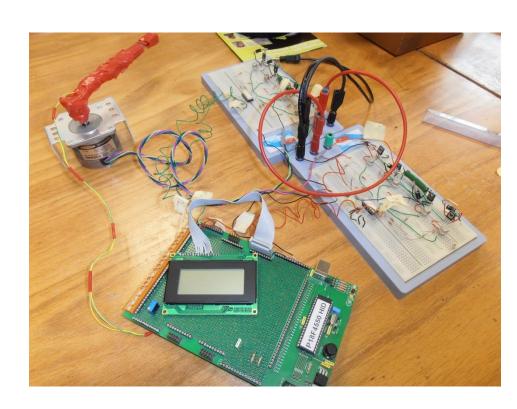

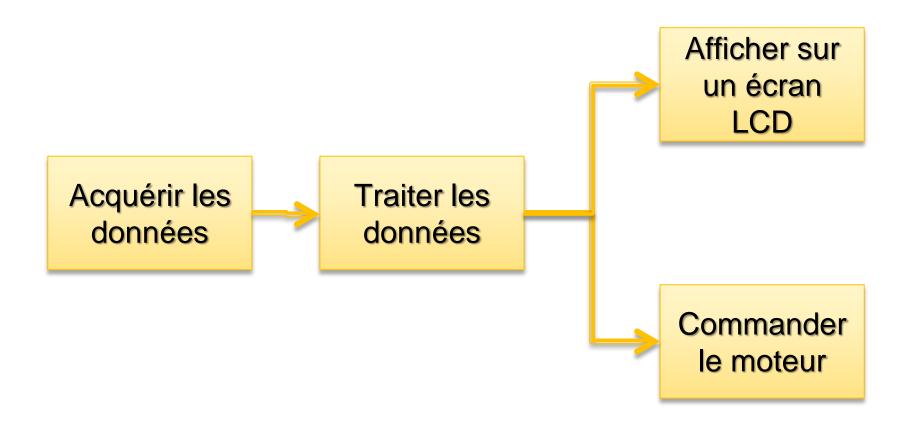

### Première étude

#### Découpage fonctionnel

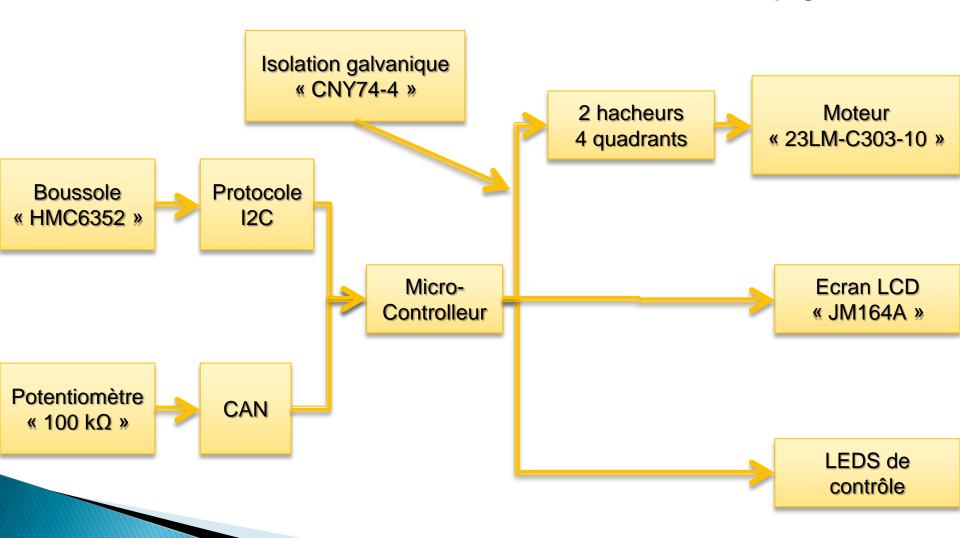

### Première étude

#### Découpage structurel

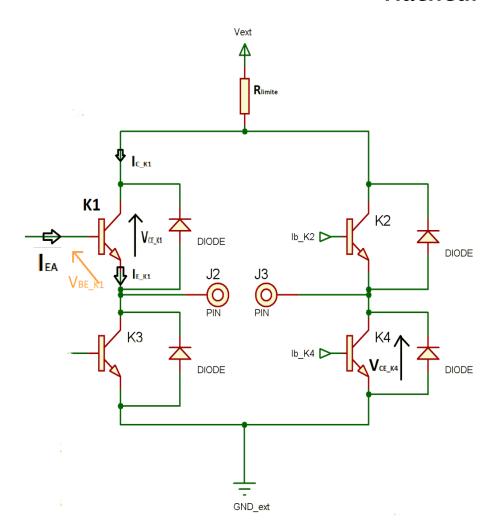

### Commande du moteur

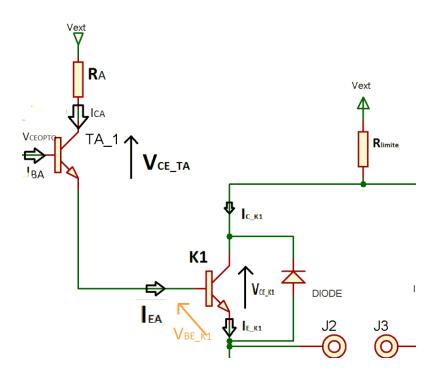

#### Hacheur

- 4 quadrants

- Transistors BD 237

- Résistance de puissance :

$$V_{\text{ext}} = (R_{\text{limite}} \times I_{\text{C}_{\text{K1}}}) + V_{\text{CE(sat)}}^{\text{K1}} + V_{\text{CE}}^{\text{K4}}$$

Diodes BY 252

### Commande du moteur

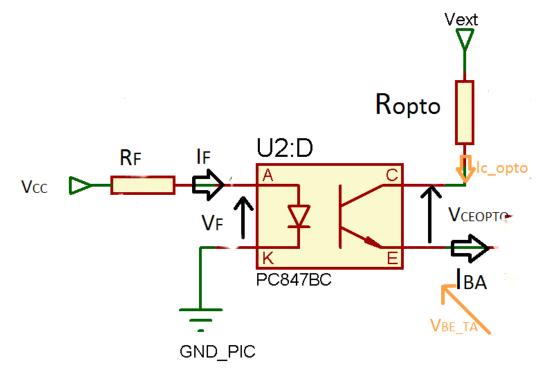

### Isolation galvanique

Optocoupleur CNY 74 – 4

### Commande du moteur

#### **Amplification**

Transistor 2N2219

### Boussole

#### Fonctionnement général

- Plusieurs modes de fonctionnement

- Calculs réguliers -> continuous mode

Plusieurs fréquences : 1Hz ; 5Hz ; 10Hz ; 20Hz

- Demande de calcul -> query mode

Après une commande 'A'

- Plusieurs types de données à recevoir

- Recevoir des coordonnées -> magnetometer mode

- Réception sur 16 bits par paquet de 8 bits

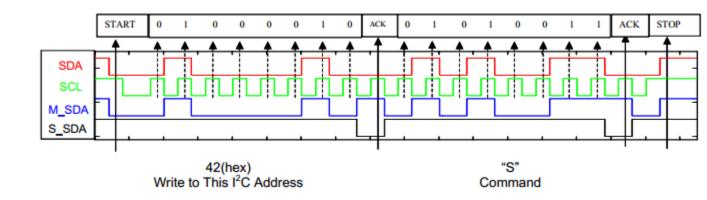

### Boussole

#### Protocole I2C

#### Emission

- Start

- Adresse

- Donnée

- ACK ou NACK

- Stop

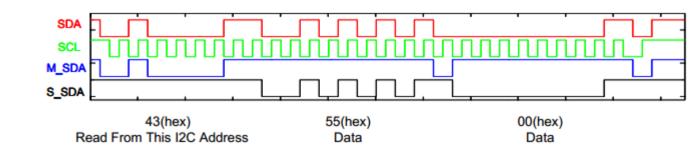

### Réception

- Start

- Adresse

- Donnée

- ACK et NACK

- Stop

### Potentiomètre et CAN

#### ADCON0

#### REGISTER 21-1: ADCON0: A/D CONTROL REGISTER 0

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 |

|-------|-----|-------|-------|-------|-------|---------|-------|

| _     | -   | CHS3  | CHS2  | CHS1  | CHS0  | GO/DONE | ADON  |

| bit 7 |     |       |       |       |       |         | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | i as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

#### • 0b00000001

```

bit 7-6

Unimplemented: Read as '0'

bit 5-2

CHS3:CHS0: Analog Channel Select bits

0000 = Channel 0 (AN0)

0001 = Channel 1 (AN1)

0010 = Channel 2 (AN2)

0011 = Channel 3 (AN3)

0100 = Channel 4 (AN4)

0101 = Channel 5 (AN5)(1,2)

0110 = Channel 6 (AN6)(1,2)

0111 = Channel 7 (AN7)(1,2)

1000 = Channel 8 (AN8)

1001 = Channel 9 (AN9)

1010 = Channel 10 (AN10)

1011 = Channel 11 (AN11)

1100 = Channel 12 (AN12)

1101 = Unimplemented<sup>(2)</sup>

1110 = Unimplemented(2)

1111 = Unimplemented(2)

bit 1

GO/DONE: A/D Conversion Status bit

When ADON = 1:

1 = A/D conversion in progress

0 = A/D Idle

bit 0

ADON: A/D On bit

1 = A/D converter module is enabled

0 = A/D converter module is disabled

```

- Note 1: These channels are not implemented on 28-pin devices.

- Performing a conversion on unimplemented channels will return a floating input measurement.

### Potentiomètre et CAN

Ob00001110

#### ADCON1

#### REGISTER 21-2: ADCON1: A/D CONTROL REGISTER 1

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 <sup>(1)</sup> | R/W <sup>(1)</sup> | R/W <sup>(1)</sup> | R/W <sup>(1)</sup> |

|-------|-----|-------|-------|----------------------|--------------------|--------------------|--------------------|

| -     | _   | VCFG1 | VCFG0 | PCFG3                | PCFG2              | PCFG1              | PCFG0              |

| bit 7 |     |       |       |                      |                    |                    | bit 0              |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-8 Unimplemented: Read as '0'

bit 5 VCFG1: Voltage Reference Configuration bit (VREF- source)

1 = VREF- (AN2)

0 = Vss

bit 4 VCFG0: Voltage Reference Configuration bit (VREF+ source)

1 = VREF+ (AN3)

0 = VDD

bit 3-0 PCFG3:PCFG0: A/D Port Configuration Control bits:

| PCFG3:<br>PCFG0 | AN12 | AN11 | AN10 | AN9 | AN8 | AN7 <sup>(2)</sup> | AN6(2) | ANS <sup>(2)</sup> | AN4 | AN3 | AN2 | AN1 | ANO |

|-----------------|------|------|------|-----|-----|--------------------|--------|--------------------|-----|-----|-----|-----|-----|

| 0000(1)         | Α    | Α    | Α    | Α   | Α   | Α                  | Α      | Α                  | Α   | Α   | Α   | Α   | Α   |

| 0001            | Α    | Α    | Α    | Α   | Α   | Α                  | Α      | Α                  | Α   | Α   | Α   | Α   | Α   |

| 0010            | Α    | Α    | Α    | Α   | Α   | Α                  | Α      | Α                  | Α   | Α   | Α   | Α   | Α   |

| 0011            | ۵    | Α    | Α    | Α   | Α   | Α                  | Α      | Α                  | Α   | Α   | Α   | Α   | Α   |

| 0100            | D    | D    | Α    | Α   | Α   | Α                  | Α      | Α                  | Α   | Α   | Α   | Α   | Α   |

| 0101            | D    | D    | D    | Α   | Α   | Α                  | Α      | Α                  | Α   | Α   | Α   | Α   | Α   |

| 0110            | D    | D    | D    | D   | Α   | Α                  | Α      | Α                  | Α   | Α   | Α   | Α   | Α   |

| 0111(1)         | D    | D    | D    | D   | D   | Α                  | Α      | Α                  | Α   | Α   | Α   | Α   | Α   |

| 1000            | D    | D    | D    | D   | D   | D                  | Α      | Α                  | Α   | Α   | Α   | Α   | Α   |

| 1001            | D    | D    | D    | D   | D   | D                  | D      | Α                  | Α   | Α   | Α   | Α   | Α   |

| 1010            | D    | D    | D    | D   | D   | D                  | D      | D                  | Α   | Α   | Α   | Α   | Α   |

| 1011            | D    | D    | D    | D   | D   | D                  | D      | D                  | D   | Α   | Α   | Α   | Α   |

| 1100            | D    | D    | D    | D   | D   | D                  | D      | D                  | D   | D   | Α   | Α   | Α   |

| 1101            | D    | D    | D    | D   | D   | D                  | D      | D                  | D   | D   | D   | Α   | Α   |

| 1110            | D    | D    | D    | D   | D   | D                  | D      | D                  | D   | D   | D   | D   | Α   |

| 1111            | D    | D    | D    | D   | D   | D                  | D      | D                  | D   | D   | D   | D   | D   |

A = Analog input

D = Digital I/O

### Potentiomètre et CAN

• 0b00100010

#### ADCON2

#### REGISTER 21-3: ADCON2: A/D CONTROL REGISTER 2

| R/W-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| ADFM  | _   | ACQT2 | ACQT1 | ACQT0 | ADCS2 | ADCS1 | ADCS0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |  |

|-------------------|------------------|-----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |  |

1 = Right justified

bit 7

0 = Left justified

bit 6 Unimplemented: Read as '0'

bit 5-3 ACQT2:ACQT0: A/D Acquisition Time Select bits

ADFM: A/D Result Format Select bit

111 = 20 TAD110 = 16 TAD 101 = 12 TAD 100 = 8 TAD 011 = 6 TAD010 = 4 TAD 001 = 2 TAD $000 = 0 \text{ TAD}^{(1)}$

bit 2-0 ADCS2:ADCS0: A/D Conversion Clock Select bits

111 = FRC (clock derived from A/D RC oscillator)(1)

110 = Fosc/64101 = Fosc/16 100 = Fosc/4

011 = FRC (clock derived from A/D RC oscillator)(1)

010 = Fosc/32 001 = Fosc/8 000 = Fosc/2

Note 1: If the A/D FRC clock source is selected, a delay of one TCY (instruction cycle) is added before the A/D clock starts. This allows the SLEEP instruction to be executed before starting a conversion.

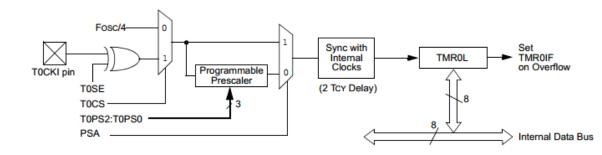

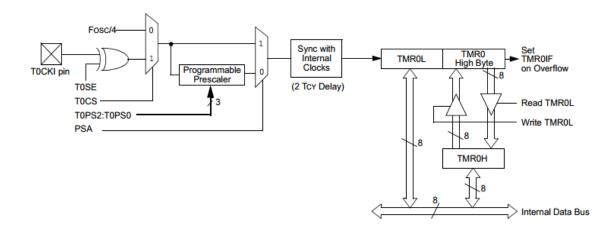

### Timer variable

- Timer pour 1 ms

- T0CON=0b00010101

- TMR0=0xFFFF 188

- 348 ms au max

- Timer pour 1 μs

- T0CON=0b01010000

- $\sim$  TMR0=0xFF 5

- 50 μs au max

### Ecran LCD

#### Commandes

- Envoyer une commande :

- $\circ$  RS = 0

- Envoyer un caractère :

- RS = 1

- Valider un envoi :

- Mettre E à 1

- Attendre

- Mettre E à 0

- Attendre

| Instruction  | RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|--------------|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Function set | 0  | 0   | 0   | 0   | 1   | DL  | N   | F   | -   | _   |

0b0001010

| Instruction                  | RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|------------------------------|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Display<br>on/off<br>control | 0  | 0   | 0   | 0   | 0   | 0   | 1   | D   | С   | В   |

0b0001100

| Instruction      | RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|------------------|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Clear<br>display | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   |

0b0000001

| Instruction       | RS | <b>R</b> /W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|-------------------|----|-------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Entry<br>mode set | 0  | 0           | 0   | 0   | 0   | 0   | 0   | 1   | I/D | S   |

0b0000110

# Bilan technique

| Partie du sujet      | Menée par               | %<br>Finalisation | Validée<br>(Oui / Non) | Remarques                                            |

|----------------------|-------------------------|-------------------|------------------------|------------------------------------------------------|

| Commande<br>moteur   | MEGHNINE /<br>REYNOUARD | 95%               | Oui                    |                                                      |

| Programmation<br>LCD | DUTEL                   | 100%              | Oui                    |                                                      |

| Programmation<br>CAN | MENDES                  | 95%               | Oui                    | Utiliser un<br>clavier mais<br>plus de<br>disponible |

| Programmation I2C    | DUTEL /<br>MENDES       | 95%               | Oui                    |                                                      |

| Finalisation glol    | oale du sujet           | 95%               | Oui                    | Manque de<br>10 heures                               |

26/06/2013

16

# Bilan de l'équipe

| Nom       | Parties Traitées   | Charge en % | Remarques               |

|-----------|--------------------|-------------|-------------------------|

| DUTEL     | Programmation      | 25%         | Aide commande<br>moteur |

| MEGHNINE  | Commande<br>moteur | 25%         | Aide programmation      |

| MENDES    | Programmation      | 25%         | Aide commande<br>moteur |

| REYNOUARD | Commande<br>moteur | 25%         | Aide programmation      |

| TOTAL     |                    | 100%        |                         |

26/06/2013

17

## Merci de votre attention